# Second Generation Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processors

Thermal/Mechanical Specifications and Design Guide

July 2020

Reference Number: 616766-007US

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel, Xeon, and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2020, Intel Corporation. All rights reserved.

# Contents

| 1 | Intro | duction                                                                                        |    |

|---|-------|------------------------------------------------------------------------------------------------|----|

|   | 1.1   | Objective                                                                                      |    |

|   | 1.2   | Scope                                                                                          |    |

|   | 1.3   | References                                                                                     |    |

|   | 1.4   | Terminology                                                                                    | 12 |

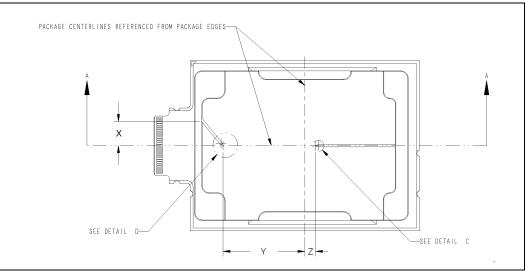

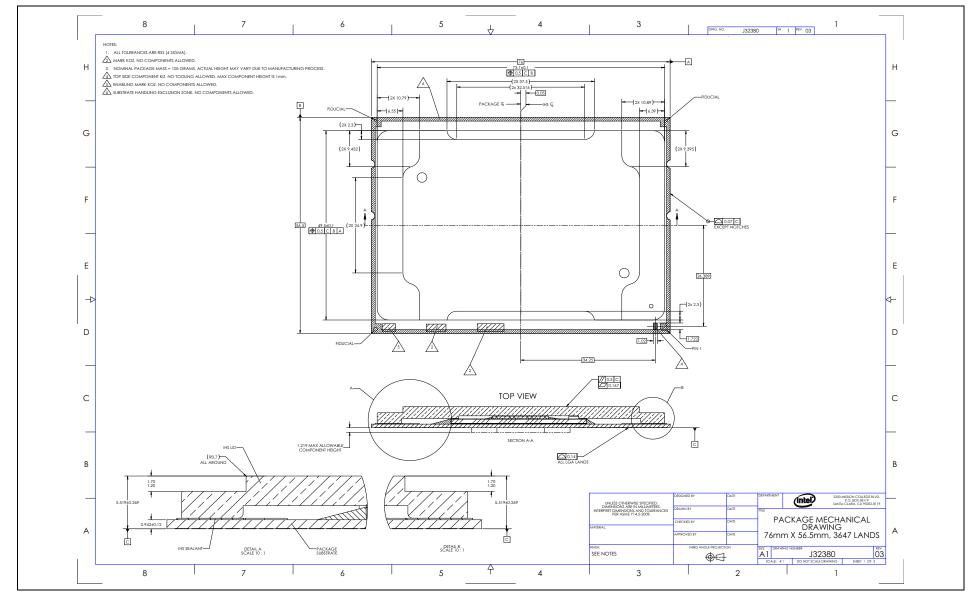

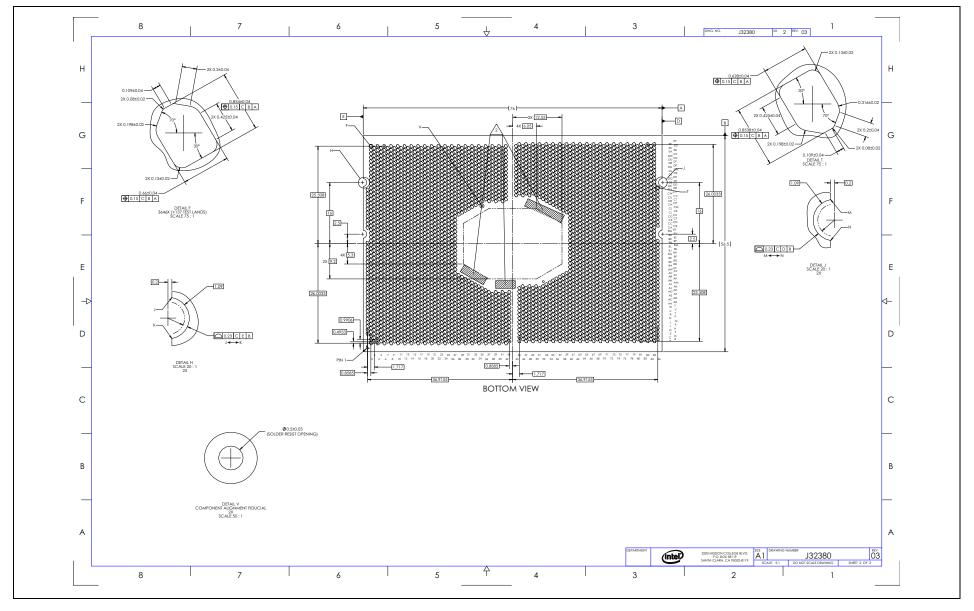

| 2 | Proce | essor Package Mechanical Specification                                                         | 14 |

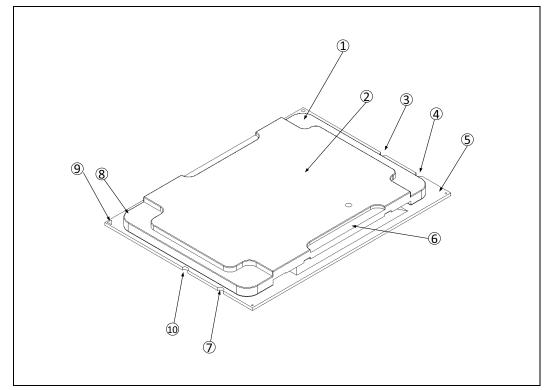

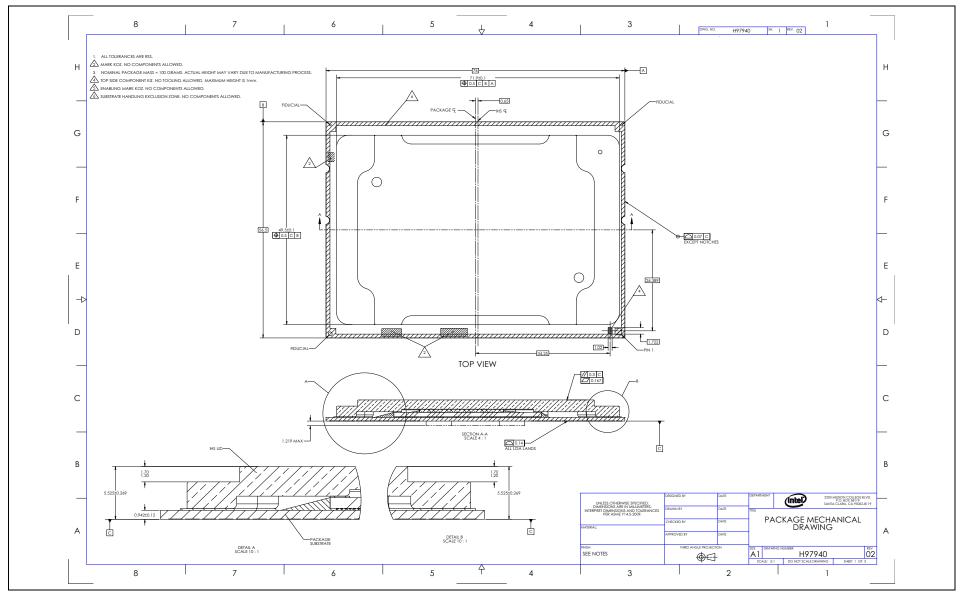

|   | 2.1   | Processor Package Description                                                                  |    |

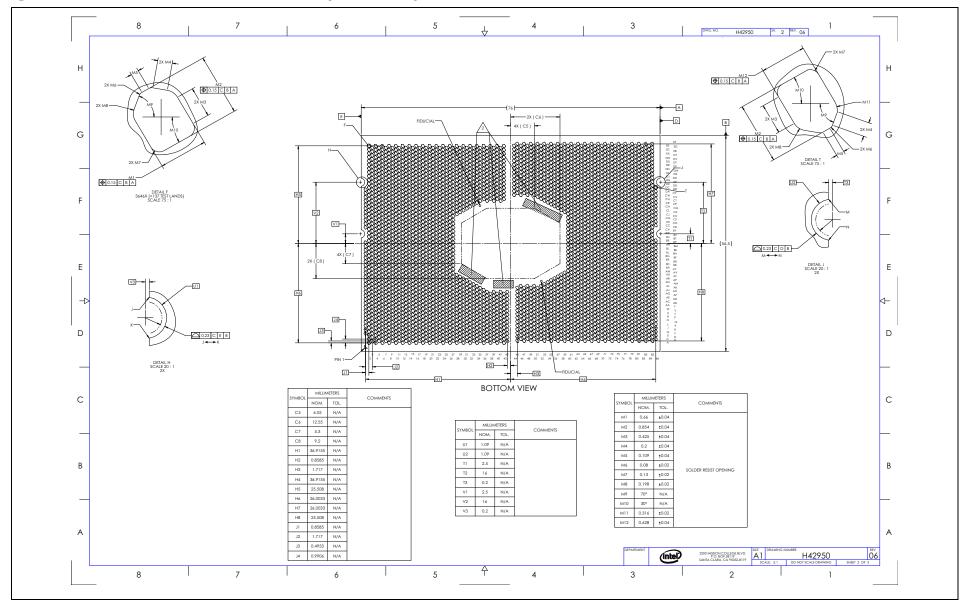

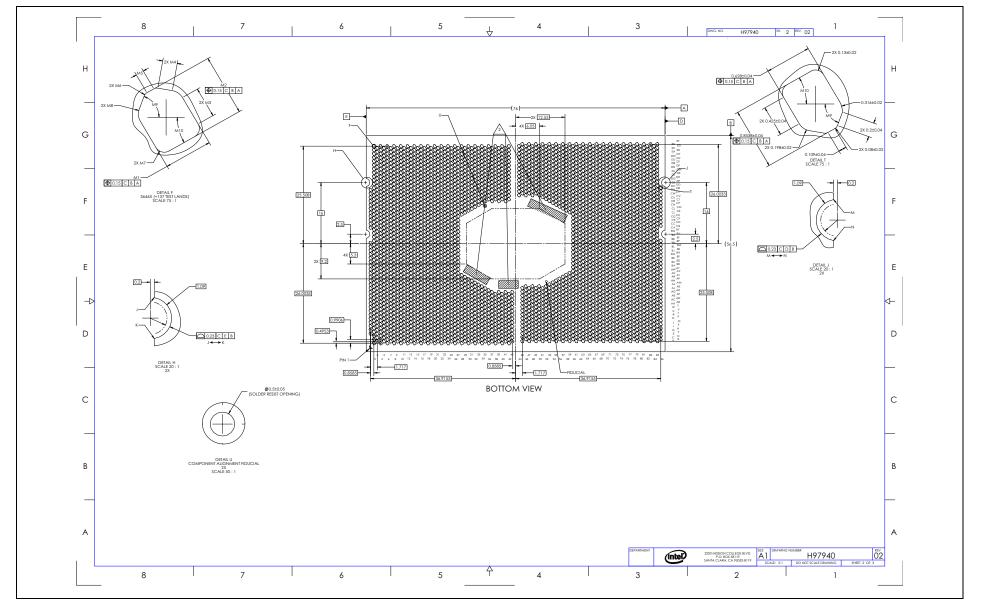

|   | 2.2   | Processor Mechanical Dimensions                                                                |    |

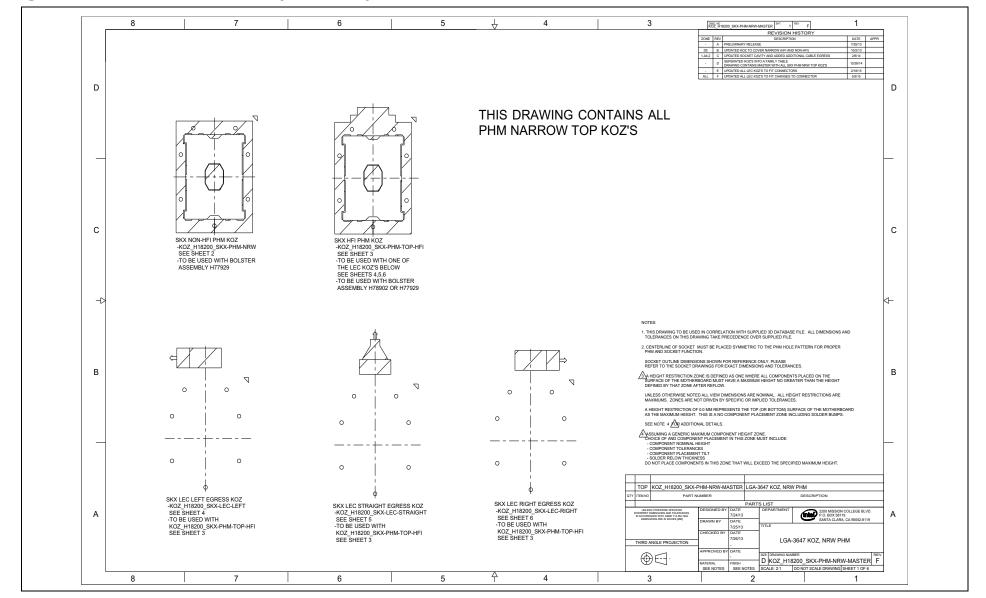

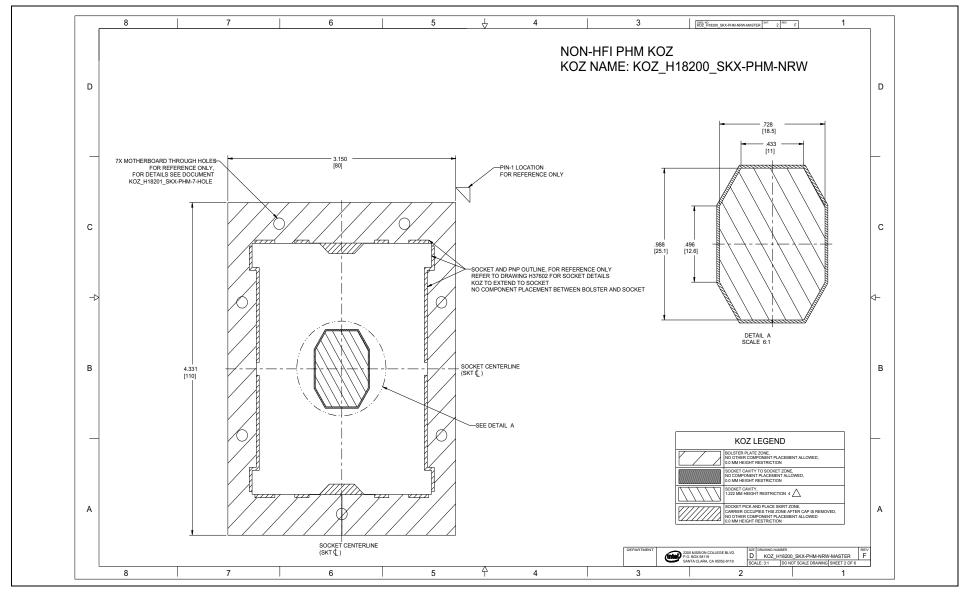

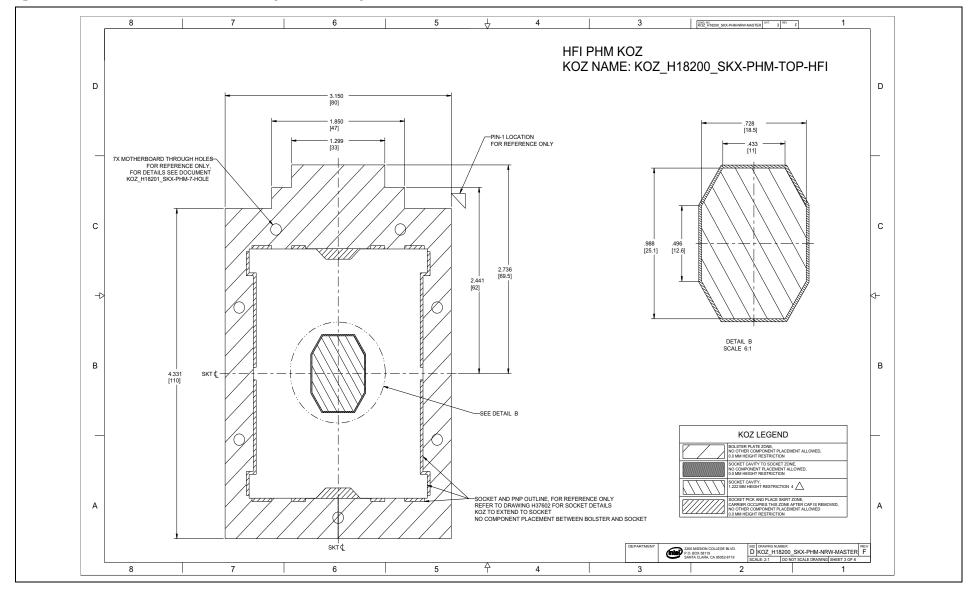

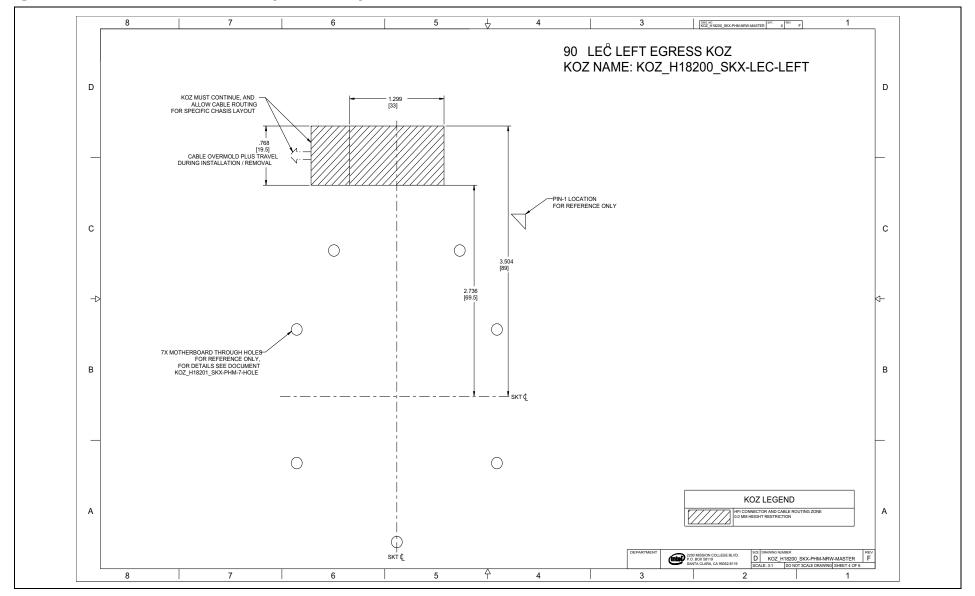

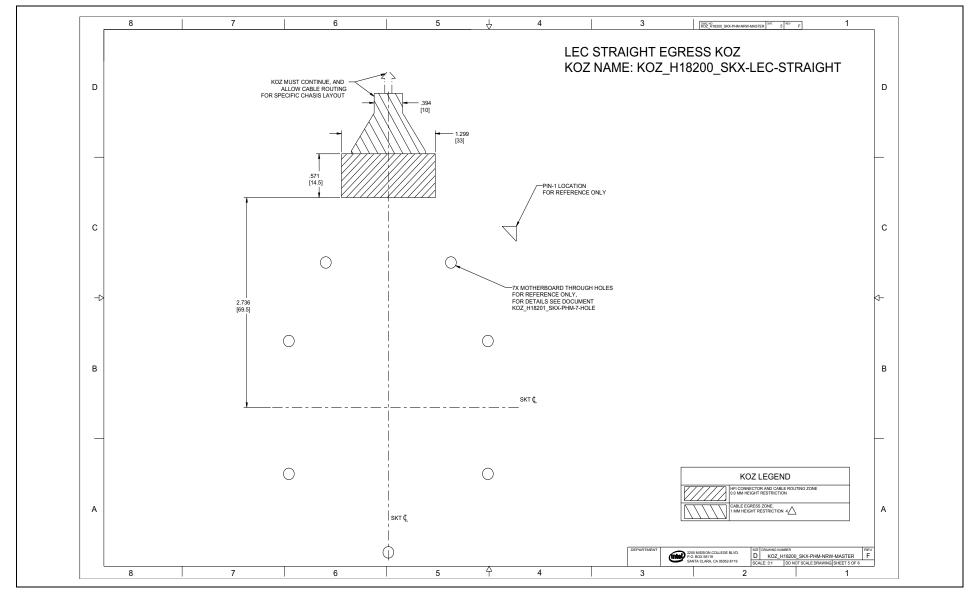

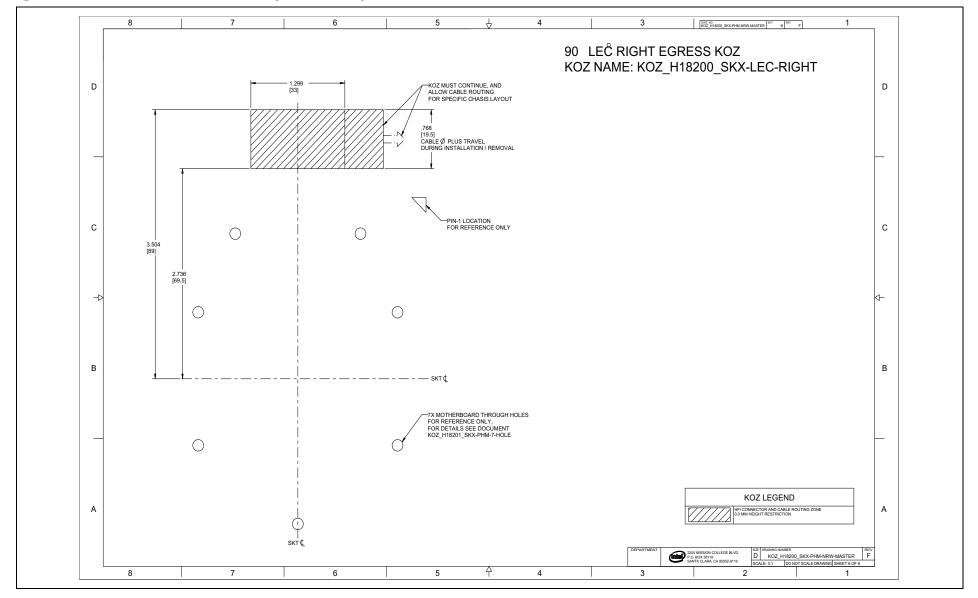

|   | 2.3   | Processor Keep-Out Zones                                                                       |    |

|   | 2.4   | Processor Mechanical Loads                                                                     |    |

|   |       | 2.4.1 Processor Component Keep-Out Zones                                                       |    |

|   | 2.5   | Processor Mass Specification                                                                   |    |

|   | 2.6   | Package Insertion Specifications                                                               |    |

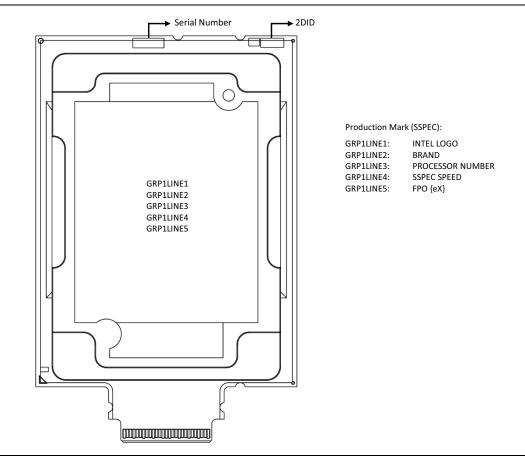

|   | 2.7   | Processor Markings                                                                             |    |

|   |       | 2.7.1 Package Handling Guidelines                                                              | 19 |

| 3 | Socke | et Specifications                                                                              | 20 |

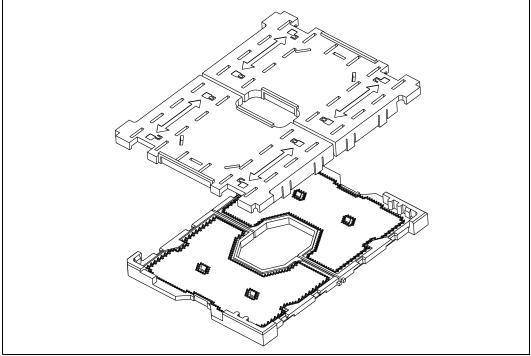

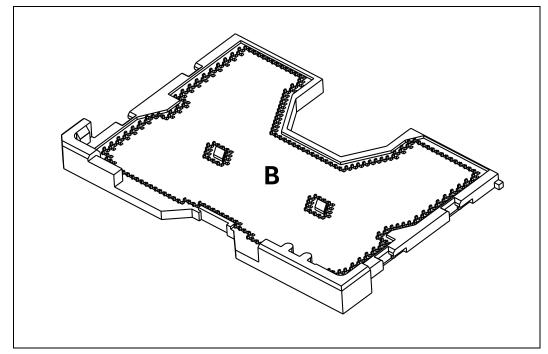

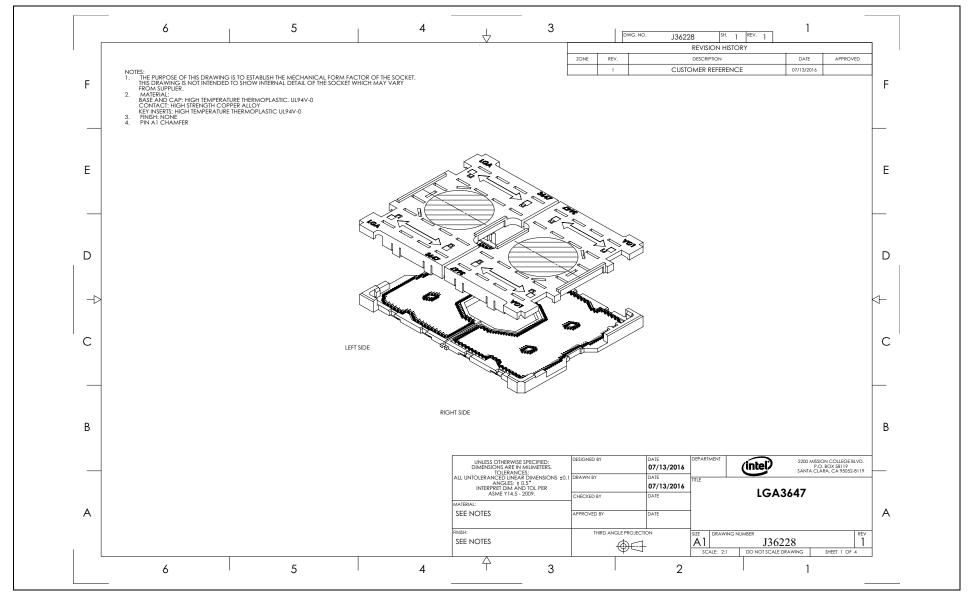

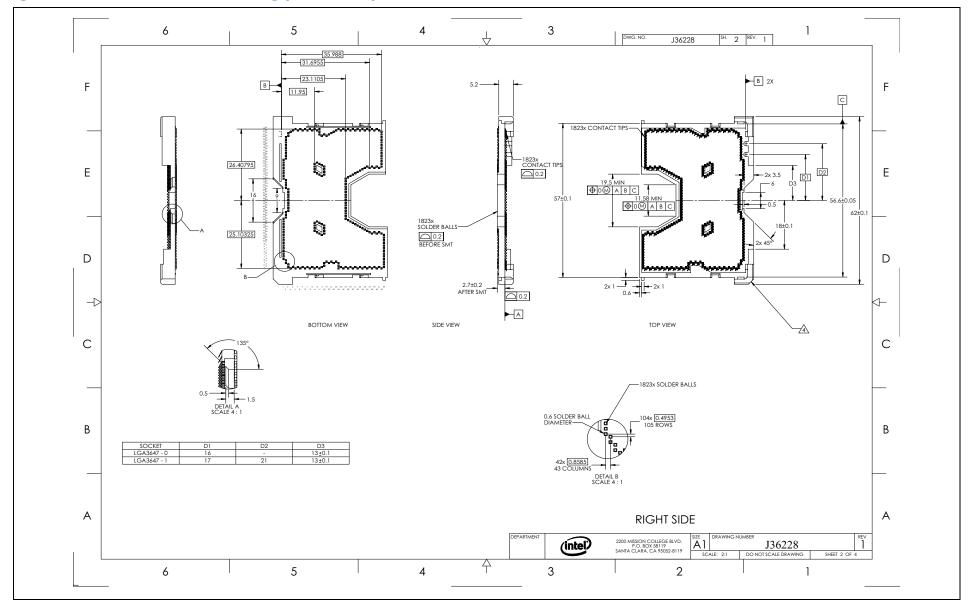

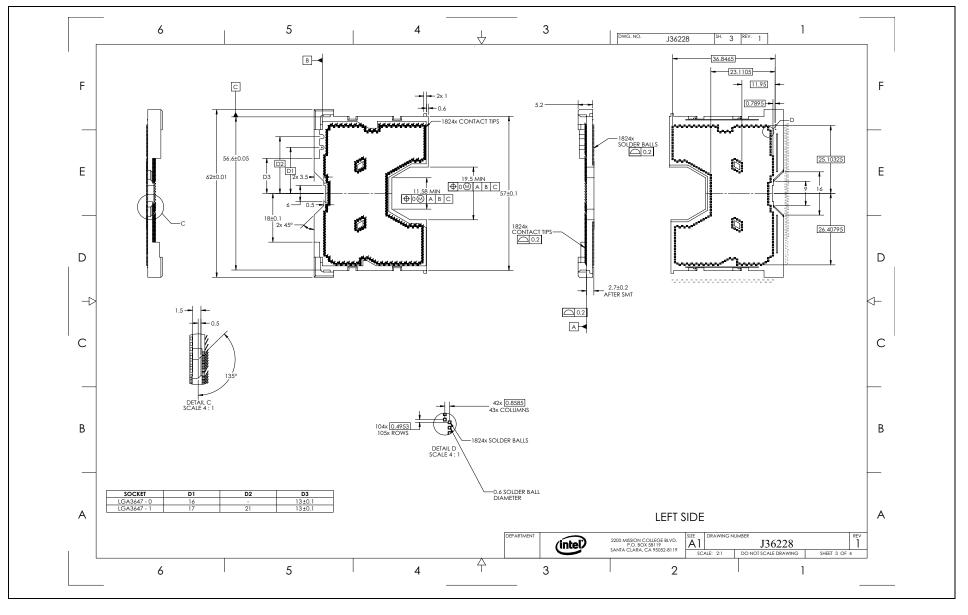

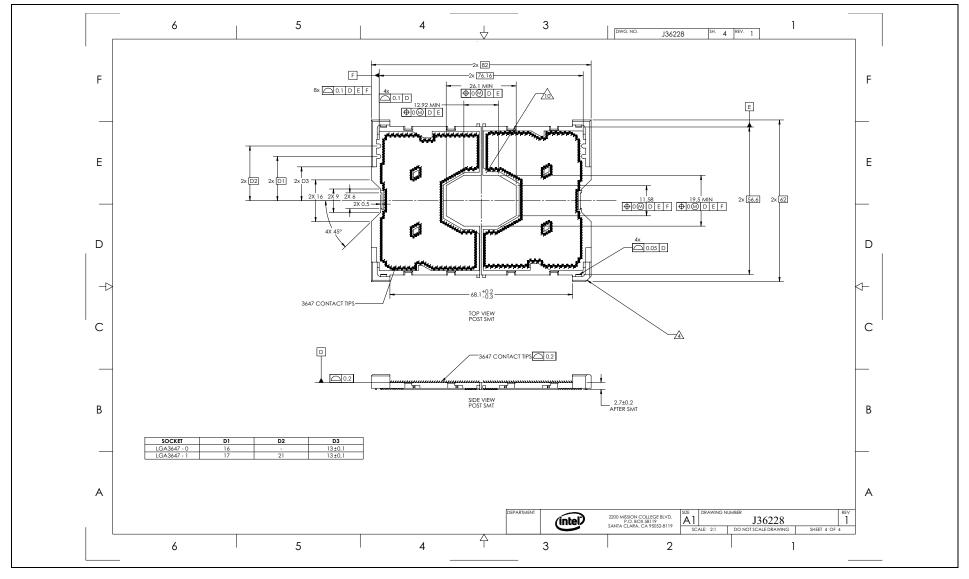

|   | 3.1   | Socket Overview                                                                                | 20 |

|   | 3.2   | Socket Features                                                                                | 23 |

|   | 3.3   | Socket Housing                                                                                 | 23 |

|   |       | 3.3.1 Housing Material                                                                         |    |

|   |       | 3.3.2 Housing Color                                                                            |    |

|   |       | 3.3.3 Package Installation/Removal Access                                                      |    |

|   |       | 3.3.4 Package Alignment/Orientation                                                            |    |

|   |       | 3.3.5 Heatsink Retention and Processor Package Carrier Compatibility                           |    |

|   |       | <ul><li>3.3.6 Markings</li><li>3.3.7 Contact Characteristics</li></ul>                         |    |

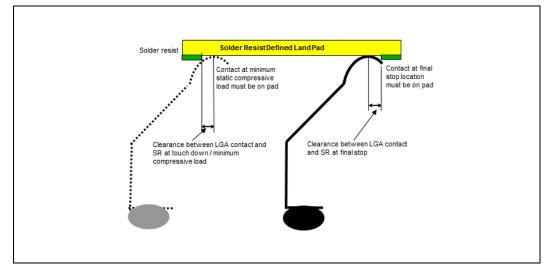

|   |       | <ul><li>3.3.7 Contact Characteristics</li><li>3.3.8 Contact/Pad Mating Location</li></ul>      |    |

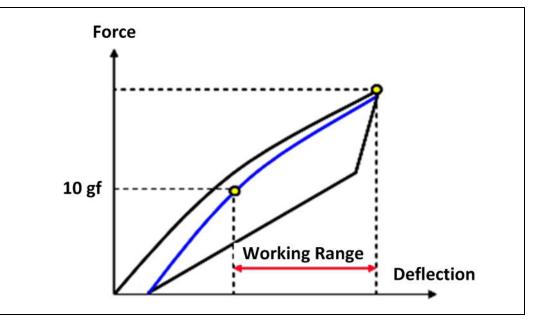

|   |       | 3.3.9 Contact-Deflection Curve                                                                 |    |

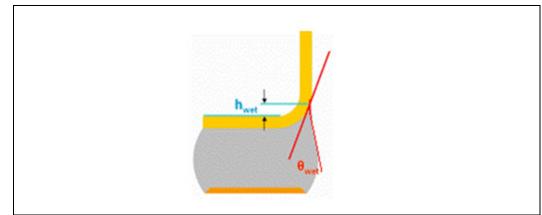

|   |       | 3.3.10 Solder Ball Characteristics                                                             |    |

|   | 3.4   | Socket Mechanical Requirements                                                                 |    |

|   | 0     | 3.4.1 Socket Size                                                                              |    |

|   |       | 3.4.2 Socket Standoffs                                                                         |    |

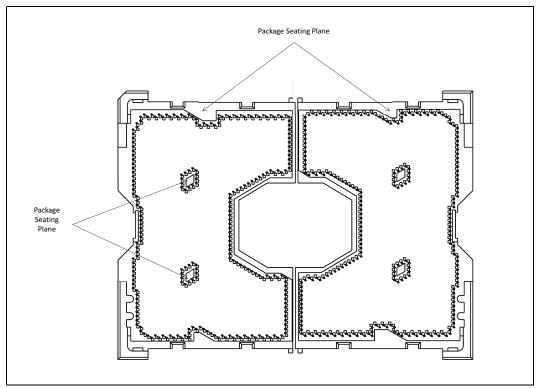

|   |       | 3.4.3 Package Seating Plane                                                                    |    |

|   |       | 3.4.4 Package Translation                                                                      | 30 |

|   |       | 3.4.5 Insertion/Removal/Actuation Forces                                                       |    |

|   |       | 3.4.6 Orientation in Packaging, Shipping, and Handling                                         |    |

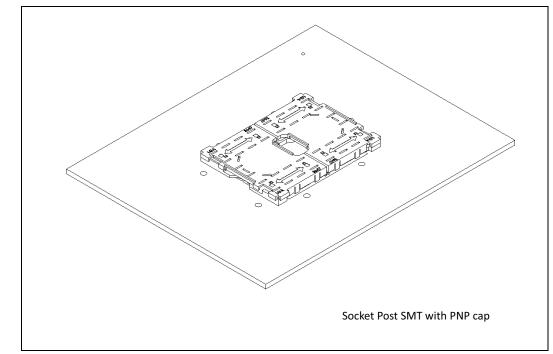

|   |       | 3.4.7 Pick and Place and Handling Cover                                                        |    |

|   |       | 3.4.8 Durability                                                                               |    |

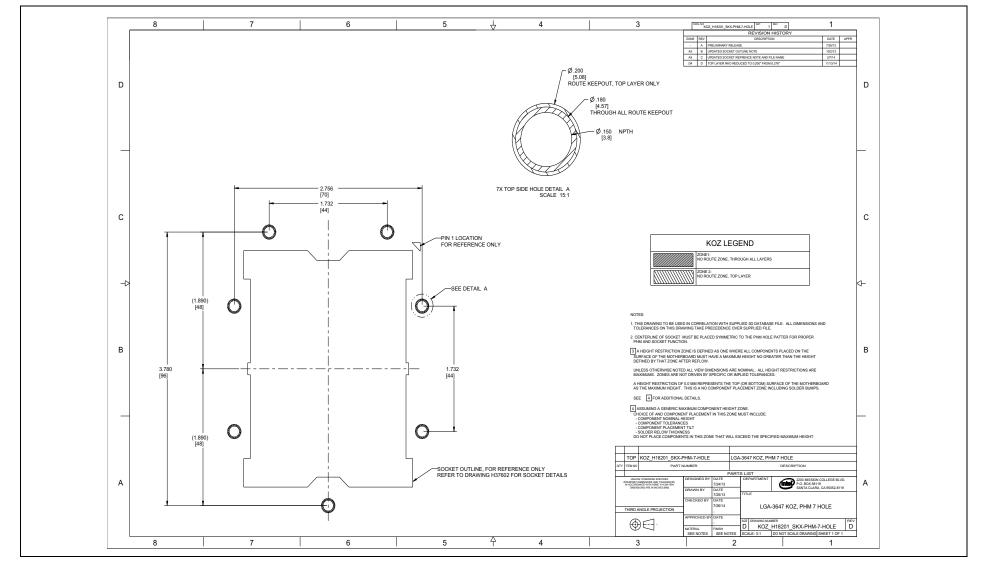

|   |       | 3.4.9 Socket Keep-In/Keep-Out Zone                                                             | 31 |

|   |       | 3.4.10 Attachment                                                                              |    |

|   |       | 3.4.11Socket Loading and Deflection Specifications3.4.12Socket Critical-to-Function Interfaces |    |

|   | 3.5   | Material and Recycling Requirements                                                            |    |

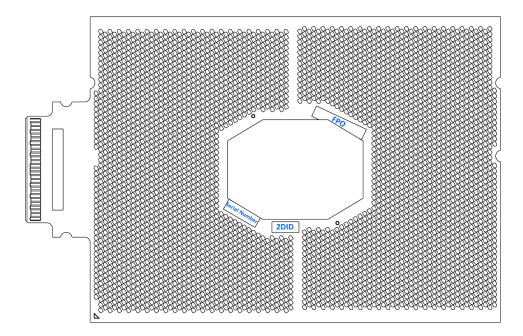

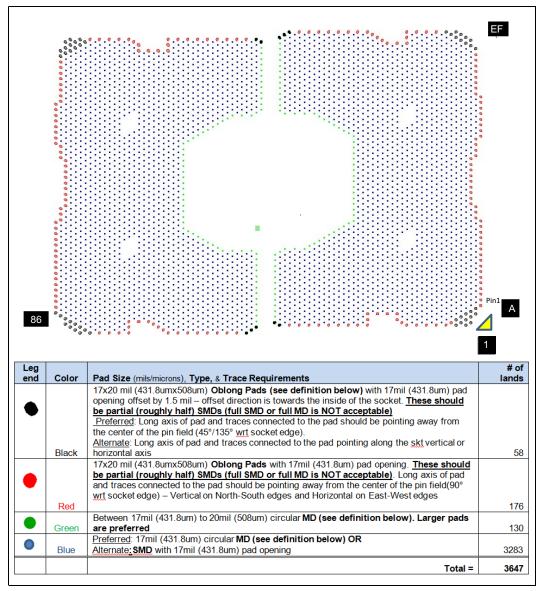

|   | 3.6   | LGA3647 Socket Land Pattern                                                                    |    |

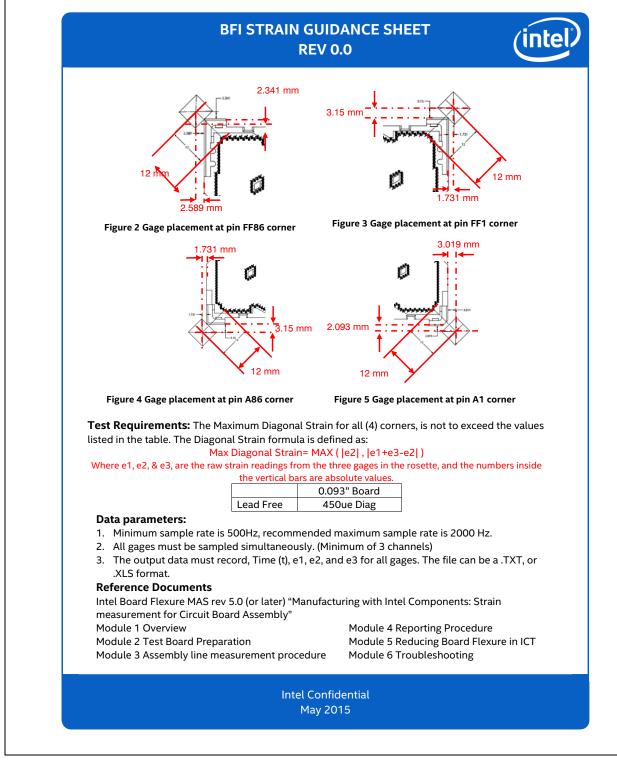

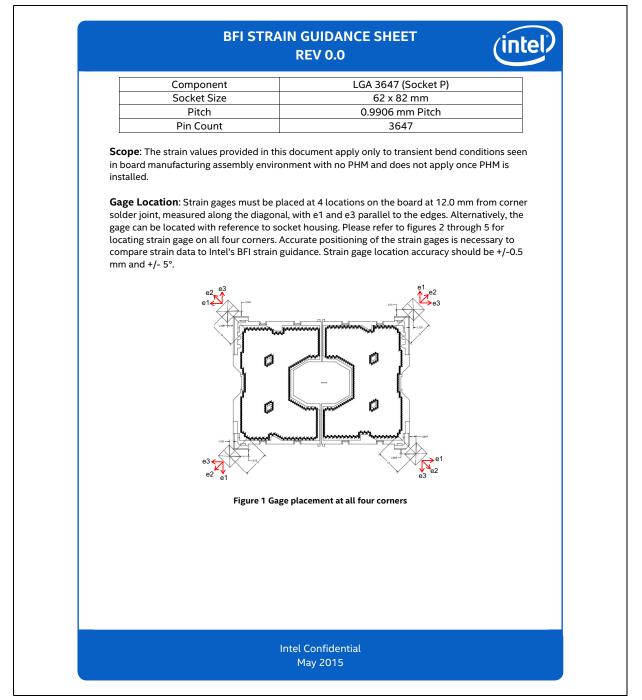

|   | 3.7   | Strain Guidance for Socket                                                                     |    |

|   |       |                                                                                                |    |

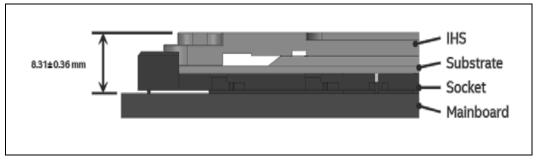

| 4 |       | age and Socket Stack                                                                           |    |

|   | 4.1   | Mechanical Load Specification                                                                  |    |

|   | 4.2   | Mechanical Design Considerations                                                               |    |

| 5 | Proce | essor Thermal Management                                                                       | 37 |

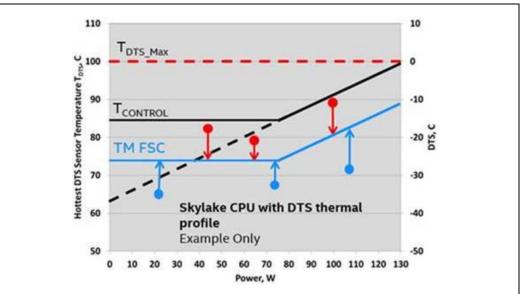

|   | 5.1   | Processor Thermal Features                                                                     | 37 |

|   |       | 5.1.1 TCC Activation Temperature                                                               | 37 |

|        |                                                                                                                 | 5.1.2                                                                                                                                                                                                                                            | Intel <sup>®</sup> Turbo Boost Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                                                                                             |

|--------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                 | 5.1.3                                                                                                                                                                                                                                            | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                |

|        | 5.2                                                                                                             | Process                                                                                                                                                                                                                                          | sor Thermal Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40                                                                                                                                                             |

|        |                                                                                                                 | 5.2.1                                                                                                                                                                                                                                            | T <sub>CASE</sub> and DTS Thermal Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                |

|        |                                                                                                                 | 5.2.2                                                                                                                                                                                                                                            | Intel <sup>®</sup> Speed Select Technology (Intel <sup>®</sup> SST) on Second Generation Intel <sup>®</sup> Xe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | on®                                                                                                                                                            |

|        |                                                                                                                 |                                                                                                                                                                                                                                                  | Scalable Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                                                                             |

|        |                                                                                                                 | 5.2.3                                                                                                                                                                                                                                            | Thermal Metrology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54                                                                                                                                                             |

|        | 5.3                                                                                                             | Process                                                                                                                                                                                                                                          | sor Thermal Management Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                |

|        |                                                                                                                 | 5.3.1                                                                                                                                                                                                                                            | Processor Thermal Solution Environmental Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                |

|        |                                                                                                                 | 5.3.2                                                                                                                                                                                                                                            | Fan Speed Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                                                                                                                                                             |

|        |                                                                                                                 | 5.3.3                                                                                                                                                                                                                                            | Thermal Excursion Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                |

| ~      | Curt                                                                                                            |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |

| 6      |                                                                                                                 |                                                                                                                                                                                                                                                  | gn Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                |

|        | 6.1                                                                                                             |                                                                                                                                                                                                                                                  | esign Consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                |

|        |                                                                                                                 | 6.1.1                                                                                                                                                                                                                                            | Allowable Board Thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                |

|        |                                                                                                                 | 6.1.2                                                                                                                                                                                                                                            | Board Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                |

|        |                                                                                                                 | 6.1.3                                                                                                                                                                                                                                            | Board Keep-Outs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |

|        |                                                                                                                 | 6.1.4                                                                                                                                                                                                                                            | Silkscreen Marking Identifying Socket and Keep-Out Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                |

|        |                                                                                                                 | 6.1.5                                                                                                                                                                                                                                            | Board Deflection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                |

|        |                                                                                                                 | 6.1.6                                                                                                                                                                                                                                            | Socket Land Pattern Guidance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                |

|        | 6.2                                                                                                             |                                                                                                                                                                                                                                                  | n Mechanical Design Consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                |

|        |                                                                                                                 | 6.2.1                                                                                                                                                                                                                                            | Processor and Socket Stack-up Height                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                |

|        |                                                                                                                 | 6.2.2                                                                                                                                                                                                                                            | Components Volumetric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                |

|        |                                                                                                                 | 6.2.3                                                                                                                                                                                                                                            | Components Mass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |

|        | 6.3                                                                                                             | •                                                                                                                                                                                                                                                | n Thermal Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |

|        |                                                                                                                 | 6.3.1                                                                                                                                                                                                                                            | Ambient Temperature (TLA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                |

|        |                                                                                                                 | 6.3.2                                                                                                                                                                                                                                            | Airflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                |

|        |                                                                                                                 |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61                                                                                                                                                             |

|        |                                                                                                                 | 6.3.3                                                                                                                                                                                                                                            | Pressure Drop (Delta P)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 04                                                                                                                                                             |

| 7      | Ther                                                                                                            |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |